## **Research Paper**

**Engineering**

# FPGA BASED MECHANISED VENDING MACHINE WITH MULTI SELECT AND CANCEL ATTRIBUTES

| B.V.S. Lakshmi | Department of Electronics and Communication Engineering                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------|

| Sindhura       | Narayana Engineering College, Nellore-524003, A.P, India                                                            |

| J. Sunil Kumar | Department of Electronics and Communication Engineering<br>Narayana Engineering College, Nellore-524003, A.P, India |

| M.V. Srinivasa | Department of Electronics and Communication Engineering                                                             |

| Reddy          | Narayana Engineering College, Nellore-524003, A.P, India                                                            |

| K. Spurthi     | Department of Electronics and Communication Engineering<br>Narayana Engineering College, Nellore-524003, A.P, India |

ABSTRACT With the advent of automation, the life style of mankind has drastically changed. POINT OF SALES (Pos) terminals have grown largely in number to satisfy the fast processing needs of the human. Vending machine is one of the POS terminals that suit the present fast life style. This work suggests the design of a Vending machine based on Finite State Machine model (Mealy) with multi select and cancel features. VHDL based implementation of the machine is proposed and implemented on a Spartan 3E FPGA board and its performance is evaluated using Xilinx ISE simulator.

### KEYWORDS: Vending Machine, Point Of Sales, Mealy Model, FPGA, Spartan 3E.

#### INTRODUCTION

Vending machine, a machine with the combination of both firmware and hardware is used to dispense items like coffee, snacks, chocolates, drinks etc on insertion of currency or credit into it. Among their numerous benefits they offer portability in their setup, avoids human intervention, offer accurate money transactions and provide a wide reach to the changing needs of the People. These can be operated round the clock so that the customer can fulfill his needs irrespective of time and conditions. Vending machines play a major role to enhance the economic growth of the food and beverages companies. Nowadays these machines are also used to dispense diamonds, gold and platinum jewels.

Previously Vending machines are designed using Microprocessor, SED and CMOS technology[1], [2]. Microprocessor based machines are complex to design, they have fixed set of instructions, debugging of those machines is a difficult task. They are less flexible to get upgraded to the changing market needs. Microprocessor based machines take long development times and hence loose market penetration. To enhance the design of these machines, the whole architecture has to be changed which is not the case with FPGA technology .Whereas FPGA based machines are flexible, reprogrammable and have large configurable logic capacity.

This work suggests the design of a Vending machine to dispense four different products using FSM (mealy) model[3]. The models also have a cancel feature so that the user can get his money back at any stage of the transaction[4]. The designed machine is then implemented on a Spartan 3E FPGA board and the functionality is tested using chip scope pro analyzer software.

#### **CONCEPT OF FINITE STATE MACHINE**

Finite state machines provide a special modeling method for sequential circuits especially for those having a well defined sequence of tasks. A large digital system that involves complex algorithms can be easily realized by Finite state machines [5]. FSM based reduces the hardware usage compared to the algorithm based machines.

In this work MEALY model of FSM [6] is used to describe the proposed Vending machine as it uses less number of states unlike a MOORE model of FSM.

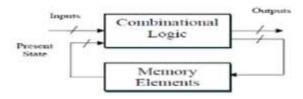

Fig 1: Mealy machine model

In mealy model of FSM, output depends both on input and the present state.FSMs are modeled using different ways like state diagrams, state tables, state equations and algorithmic state machine charts i.e. ASM charts. In this work a state diagram representation of the proposed machines is developed as per the required functionality.

#### **VENDING MACHINE OPERATION**

- 1) The machine stays in the initial state until the currency is inserted.

- 2) User inserts money of certain denomination which the machine accepts.

- 3) User selects the desired product among which the machine contains.

- 4) The selected product is dispensed to the user, along with the change if any

- 5) The user can cancel his request at any time of processing and the inserted money is returned back.

#### **DESIGN METHODOLY**

#### I.DESCRIPTION OF THE PROPOSED MACHINE

Initially all the states of the machine are analyzed and a state diagram is constructed. The state diagram should consist of all possible states and the transition conditions for moving from one state to the other.

The machine can dispense four different products i.e. snacks, coffee, kinleyand cold drink. The machine accepts currency of single denomination i.e. rs 10\- .The machine also have a coin return input to get the inserted money back.

#### **Table I: Inputs & Outputs**

| SIGNALS      | DIRECTION | DESCRIPTION              |  |

|--------------|-----------|--------------------------|--|

| Snack_in     | Input     | Snacks                   |  |

| Coffee_in    | Input     | Coffee                   |  |

| Kinley_in    | Input     | Kinley                   |  |

| Colddrink_in | Input     | Cold drink               |  |

| Rs10         | input     | 10/-                     |  |

| Return_in    | Input     | For cancel of request    |  |

| Snack_out    | Output    | Snacks                   |  |

| Coffee_out   | Output    | Coffee                   |  |

| Kinley_out   | Output    | Kinley                   |  |

| drink_out    | Output    | cold drink               |  |

| Return_out   | Output    | Give inserted money back |  |

| Q0           | output    | change                   |  |

**Table II: Products and Their Prices**

| PRODUCT   | PRICE |

|-----------|-------|

| Snacks    | 20    |

| coffee    | 20    |

| Kinley    | 30    |

| Colddrink | 40    |

#### II. DETAILS OF DESIGNING THE MACHINE

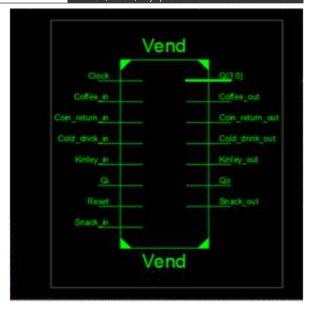

The machine can vend four different products i.e. snacks, coffee, kinley water bottle and cold drink. It has a reset signal which makes the machine to go the initial for the next selection. Snack\_in is used for the selection of snacks, coffee\_in for coffee, kinley\_in for kinley bottle and drink\_in for cold drink. Rs 10 is the input for the insertion of money. Return\_in is an input Used when the user wants to get all his inserted money back. Snack\_out, coffe\_out, kinley\_out, drink\_out are the outputs to dispense the respective products.Q0 is an output used to provide change if extra money is inserted than required for a particular product [7].

Products and their prices are shown in Table2. The machine also has a clock and reset signals as inputs. The Machine works during the raising edge of the clock and by the triggering of reset. Reset button makes the machine to go the initial state after the dispense of product for the next selection.

Fig 2: Flow Chart for the proposed machine

The product is dispensed in single clock cycle. Only one input among the others can be active at any time. If none of the inputs are active, then the machine stays in the initial state.

After analyzing inputs and outputs, an FSM is constructed for the proposed vending machine. This is done by using Xilinx ISE tool (9.1) which has a provision for designing of a state diagram. Then the constructed state diagram is compiled. The tool provides an option of converting the designed state diagram into HDL code. The generated code gets saved as a notepad file in the original project module.

#### III. DESCRIPTION OF STATE DIAGRAM

The state diagram of the proposed machine consists of twelve states i.e. A,B,C,D,E,F,G,H,I,J,K and L where state A corresponds to initialize state. When the currency is inserted the machine goes from state A to B.

State B: Any of the below can happen

Want to get money back, return\_in signal is made active and the machine goes to state C. Inserted money is returned and machine goes to initial state

State C: When the machine is in state C, it returns all the inserted money in the machine and goes back to the initial state.

State D: (20 rupees inserted in total)

- 1) Want to get money back, return\_in signal is made active and the machine goes to state C. Inserted money is returned and machine goes to initial state.

- 2) Snack\_in is made active, machine goes to state E, dispenses snacks and goes back to state A.

- 3) Coffee\_in is made active, goes to state F, dispenses coffee and goes back to state A.

- 4) Another 10|-rupee is inserted, goes to state G and waits.

State E: When the machine is in state E, snacks is dispensed and the control goes to the initial state (A).

State F: Machine dispenses coffee and returns to state A

State G: (total 30 rupees inserted)

- 1) Want to get money back, return\_in signal is made active and the machine goes to state C. Inserted money is returned and machine goes to initial state.

- 2) snack\_in made high , goes to state K , return change of rupees 10, goes to state E, dispenses snacks and goes back to state A.

- 3) coffee\_in made high, goes to state F, return change of rupees 10, goes to state F, dispenses coffee and goes back to state A.

- 4) kinley\_in made high, machine goes to state H, dispenses kinley bottle and goes back to state A.

- drink\_in is made high, goes to state I, dispenses cold drink and goes back to state A.

$State \ H: Machine \ dispenses \ kinley \ bottle \ and \ goes \ back \ to \ state \ A.$

$State \ l: Machine \ dispenses \ cold \ drink \ and \ returns \ to \ initial \ state.$

$State\,K, J: Machine\,dispenses\,extra\,amount\,inserted$

#### STATE DIAGRAM OF THE PROPOSED MACHINE

After creating the state diagram in state cad tool of Xilinx ISE(9.1) VHDL code [8] is generated and simulated using Xilinx ISE (14.2) [9]. The functionality and timing behavior of the proposed machine are then checked using the simulated waveforms.

The proposed machine is then implemented on SPARTAN-3E FPGA kit [10] and hardware debug is done using chip scope pro logic analyzer software.

## RESULTS OF SIMULATION RESULT1

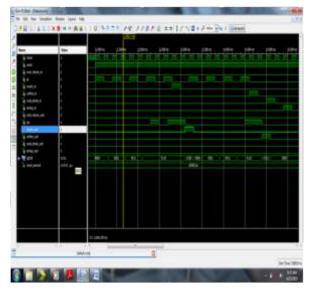

Fig 3: simulated waveform when snack\_in, coffee\_in are high

The user has inserted total of five 10\- rupees one after the other with a waiting time of 200 ns between each insertion. After that snack\_in is selected. The extra money of 30\- is returned and the selected product i.e. snacks is dispensed with a waiting time of 100 ns after the selection of product. Again the user has inserted a total of 40 rupees and selected coffee. Extra 20\- is returned back and coffee is dispensed.

#### **RESULT2**

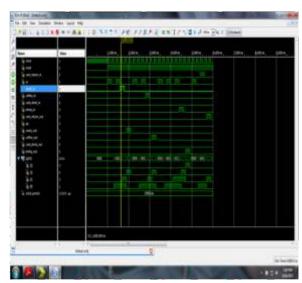

The user has inserted two 10\- one after the other. snack\_in is made high. Snacks are dispensed after 100ns. Again two 10\- are inserted, coffee\_in is made high. Coffee is dispensed after 100ns and then 30\- is inserted, kinley\_in is made high. Kinley water bottle is dispensed with a delay of 100ns. Another 10\- is inserted, return\_in is made high. After 100ns inserted 10\- is given back.

Fig 4: simulated waveform when snack\_in, coffee\_in,kinley\_in and return\_in are high

Fig 5: schematic representation of the machine

**Table III. Device Utilization Summary**

| Logic Utilization             | Used | Available | Utilization |

|-------------------------------|------|-----------|-------------|

| Number of slices              | 19   | 4656      | 0%          |

| Number of slice flip<br>flops | 14   | 9312      | 0%          |

| Number of 4 input<br>LUTs     | 25   | 9312      | 0%          |

| Number of bonded IOBs         | 18   | 232       | 7%          |

| Number of GCLKs               | 1    | 4         | 4%          |

#### CONCLUSION

The design of proposed multi select smart vending machine with cancel feature based on FINITE STATE MACHINE is verified in terms of both functionality and timing behavior using Xilinx ISE simulator (14.2). The design is implemented on Spartan-3E tool and debugged using chip scope pro logic analyzer. The algorithm of the designed machine is flexible to get upgraded to additional product dispensing. This work is later extended to layout design of the proposed machine and also analyzing the power consumed by the machine.

| Volume-4, Issue-5, May Special Issue-2015 • ISSN No 2277 - 8160    |  |  |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|--|--|

| volume=4, issue=5, inay special issue=2015 • issin inu 2277 • 6100 |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

|                                                                    |  |  |  |  |  |  |  |

**REFERENCES**

[1] Biplab Roy & Biswarup Mukherjee (2010) "Design of Coffee Vending Machine using Single Electron Devices" Proceedings of 2010 International Symposium on Electronic System Design. Pp38-43. [2] C.J. Clement Singh, K. Senthil Kumar, Jayanto Gope, Suman Basu & Subir Kumar Sarkar (2007) "Single Electron Device based Automatic Tea Vending Machine" proceedings of International Conference on Information and

CommunicationTechnology in Electrical Sciences (ICTES2007), pp891–896. [3] Peter Minns& Ian Elliott, "FSM-based Digital Design using Verilog HDL", John Wiley & Sons Ltd 2008. [4] Mealy, G. H., "A method for synthesizing sequential circuits," Bell System Tech. J., Vol. 34, No. 5, pp. 1045–1079, 1955. [5] Ana Monga, Balwinder Singh "Finite State Machine based Vending Machine Controller with Auto-Billing Features", International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No. 2, April 2012. [6] Iuliana CHIUCHISAN, Alin Dan POTORAC, Adrian GRAUR, "Finite State Machine and VHDL coding. [7] Golson, S., "State Machine Design Techniques for Verilog and VHDL", Synopsys Journal of High-Level Design, pp. 1-2, 1994. [8] Muhammad Ali Qureshi, Abdul Aziz, Hafiz FaizRasool, "Design and Implementation of Automatic Train Ticketing System Using Verilog HDL", 2012. [9] J. Bhaskar, "VHDL primer," Third Edition. [10] Pong P. Chu, "FPGA Prototyping using Verilog HDL-Xilinx Spartan-3 Version", John Wiley & Sons, 2008.